Home > finite state machines > FSM Applications > UART Transmitter Design

UART Transmitter Design

UART Transmitter Design :

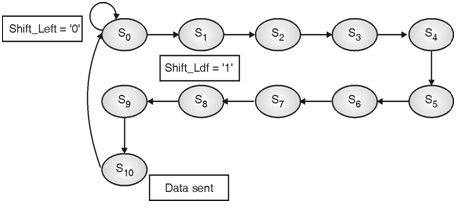

The UART transmitter receives 8 bit parallel data and converts it into a 10 bit serial data adding one start and one stop bit. I have used a finite state machine to implement a behavioral model for transmitter section. This machine has eleven states S0 to S10. State 0 is idle state when transmitter is waiting for the data to be high on input lines. As soon as “Shift_LdF†signal goes low (which signals incoming data), the state machine switches to state S1 and disables “XmitMT†signal (which signals receiver that data is being sent) while concurrently loading a ten bit logic vector's first bit with the “start†bit “0†and rest with “0â€. The machine then switches to state S2 and S3 and so on at every rising edge of clock there by tapping data to different bit of logic vector keeping other bits “0â€. This results in a condition where in at each clock cycle only one bit of vector will contain desired information. In S10 “XmitMT†signal is raised and after that all bits of bit vector are ORed to result in output. In short each state sets one bit while resetting others.

Present state Next state Input

shift_LdF Output

XmitMT Sg

0000 0001 1 1 100000000

0000 0000 0 0 x

0001 0010 x 0 000000000

0010 0011 x 0 0(D7)00000000

0011 0100 x 0 00(D6)0000000

0100 0101 x 0 000(D5)000000

0101 0110 x 0 0000(D4)00000

0110 0111 x 0 00000(D3)0000

0111 1000 x 0 000000(D2)000

1000 1001 x 0 0000000(D1)00

1001 1010 x 0 00000000(D0)0

1010 0000 x 0 0000000001

Note- Serial_data is then stored result of Sg(0) to Sg(9)