System-On-Chip

In order to control the clock skew the clock distribution techniques are used. The main problem in clock distribution is the availability of capacitance which plays important role in clocked systems. Therefore, normally in clock lined semiconductor integrated circuits the integrated circuit designers put significant efforts to minimize the gate capacitance. In order to produce sharp transitions, Clock distri¬bution is a challenging task for large capacitive load.

Fig_Clock Distribution

Fig_Clock Distribution

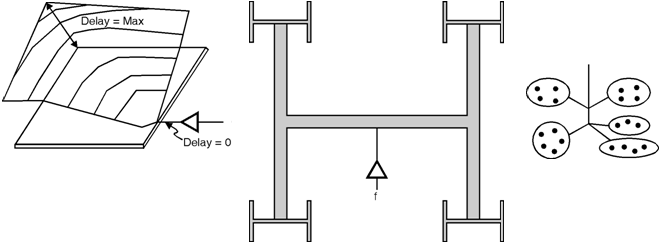

Figure above shows a simple map of clock delay vs position. In this map, the height on the surface shows the clock delay. The various techniques used to improve the clock distribution are,

• Physical design : In this technique the layout of the semiconductor integrated circuit is designed in such a way that the clock delay is minimum.

• Circuit design : In circuit design technique the circuits driving the clock distribution are designed in such a way that the clock delay is minimum.

Further, figure shows H tree, in this case the widths are adjusted in such a way that, the variations in the load capacitance are as minimum as possible. Further, the widths are also adjusted in such a way that the skew throughout the H-tree is equal. Further, in order to increase the drive capability, buffers are also added into the H-tree network. The H-tree network is considered as a top-down technique in which the floorplan of the H-tree finds the floorplan of the logic. As shown in figure balanced tree clock network created by using placement and routing in an integrated circuit. In this case the clustering is used to guide the placement. In order to minimize the clock skew the tree balanced.