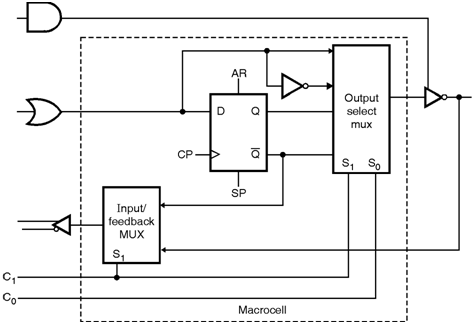

The PLDs such as PLAs, PALs are simple PLDs. The programmable logic devices such as PLAs and PALs are having less number of inputs, product terms, and outputs. Therefore for logic circuits that requires more inputs and outputs SPLD chips are used. The most popular SPLDs are PALs produced by Advanced Micro Devices (AMD) e.g. 16R8 and 22V10. In SPLD the macrocell should be configured by programming the state of configuration bits. The configuration bits allows macrocell input, in the form of sum of products. The programmable macrocell have feedback to use as input to the logic array. The feedback is directed from the register. Further, output-enable product term is programmed so that output is always disabled which allow I/O to be used as a device input. Figure below shows the structure of SPLD. Here, the top and bottom macrocells are allocated 8 product terms, the middle macrocells are allocated 16 product terms, and the others are allocated 10, 12, or 14, depending on location. SPLDs are available with AMD, Altera, ICT, Lattice, Cypress and Philips-signetics etc.

Fig_Simple Programmable Logic Devices

Fig_Simple Programmable Logic Devices