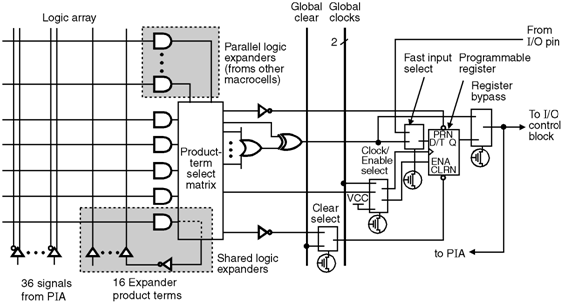

To realize logic functions.in MAX 7000 devices EEPROM cells are used. Because of involvement of iterations the MAX 7000 devices are reprogrammed. MAX 7000 family devices are combined into groups known as logic array blocks. In order to build complex logic circuits, the macrocell is supplemented product terms. The MAX 7000 family provides programmable speed/power optimization. The features of this family of CPLDs are, 1) High-performance second-generation MAX architecture, 2) Built-in JTAG boundary-scan test, 3) Complete EPLD family, 4) Programmable macrocell flip-flops with individual controls and 4) Programmable power-saving mode in each macrocell. The MAX 7000 architecture includes, 1) Logic array blocks 2) Macrocells, 3) Expander product terms, 4) Programmable interconnect array and 5) Input/Output control blocks. The MAX 7000 architecture is based on high performance logic array blocks consist of 16-macrocell arrays. Logic array blocks are linked together with the programmable interconnect array. The MAX 7000 macrocell configured for sequential and combinational logic operation. In MAX 7000 macrocell the combinational logic is implemented in the logic array and provides five product terms per macrocell. Here, logic is routed between logic array blocks to programmable interconnect array. Signals required by each logic array block are routed from the programmable interconnect array into the logic array block. EEPROM cell controls one input to a 2-input AND gate, and selects a programmable interconnect array signal to drive into the logic array block. The I/O control block for the MAX 7000 family leads to I/O pin configuration for input, output, or bidirectional operation. The I/O pins has tri-state buffer to control global output signals. The I/O control block of devices has two global output enable signals.

Altera-FLASH-logic-CPLDs

Altera-FLASH-logic-CPLDs