Home > VHDL > Sequential Statements > Process Statement

Process Statement :

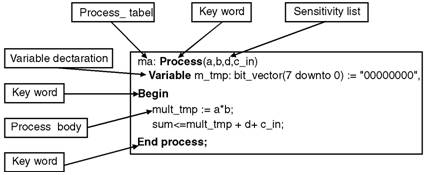

PROCESS is a sequential execution part of VHDL code. This part contains IF, WAIT, CASE or LOOP statements. The PROCESS should be installed in the main program code and should be executed every time when the event occures on a signal present in the sensitivity list. VARIABLES must be declared in the declarative part of the PROCESS before the word BEGIN. The use of a label in the PROCESS is optional. Further, in order to construct synchronous circuit, clock is necessary. To detect signal change EVENT attribute is used. e.g. if clk signal to be checked, then clk'EVENT returns TRUE when a change on clk occurs. the sequential statements within each process are executed one by one. The process statement shows the design behavior. The declarative part of process declares subprograms, types, subtypes, constants, variables, files, aliases, attributes, use clauses and group declarations. It is not allowed to declare signals or shared variables inside processes. Figure below shows the parts of process statement.

The syntax is

[ label: ] process [ ( sensitivity_list ) ]

begin

{ sequential_statement }

end process [ label ] ;

Sensitivity List :

The sensitivity list specify the signals and inputs on which events occurs. it is specified at right side of the process word.

Ø Example 1:

process (rst,clk)

begin

if rst = '1' then

Q_reg <= "00000000";

elsif (clk = '1' and clk'event) then

if (load = '1') then

Q_reg <= data_in;

else

Q_reg <= Q_reg (1 to 7) & Q_reg(0);

end if ;

end if;

end process;

Ø Example 2:

entity mod_8_counter is

port (CL : in std_logic;

C_IN : in INTEGER range 0 to 7;

C_OUT : out INTEGER range 0 to 7);

end mod_8;

architecture arch_pro of mod_8_counter is

begin

process (C_IN, CL)

begin

if (CL = '1' or C_IN = 7) then

C_OUT <= 0;

else

C_OUT <= C_IN + 1;

end if;

end process;

end arch_pro;