Home > VHDL > Introduction > VHDL Simulation

VHDL Simulation :

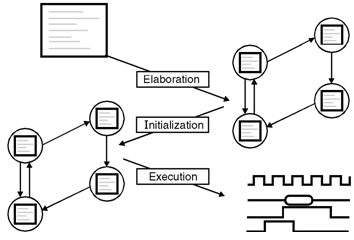

Fig. 5.25.1 : VHDL Simulation Flow

The simulation of a VHDL code is carried out in three parts. First, the simulation model is created in the elaboration phase. In the initialization phase a starting value is assigned to all the signals. The model itself is executed in the execution phase.

1) Elaboration :

During elaboration design elements are created. The processes and concurrent statements of the whole design are combined in a communication model. These model lists, which process can be activated which one creates i.e. some sort of netlist.

2) Initialization :

The initial values of all signals are assigned in the initialization phase. In the case of the type STD_ULOGIC based types this is an 'u' for uninitialized. Hence the designer can deduce from an 'u' in the simulation waveform, that there has never been assigned a value to the corresponding signal.

3) Execution :

(1) The actual simulation of the design behaviour takes place in the execution phase. By means of test bench processes, the VHDL model is provided with stimuli. The individual signals of the model can then be viewed and checked in the waveform window.