Home > VHDL > Concurrent Statements > Component Instantiation

Component Instantiation Statements :

Component instantiation is the important statement in structural modeling of the VHDL coding. The component instantiation statement shows the subsystem declared in the component declaration part of the VHDL code. Component instantiation has the instantiated unit and actual values for generics and ports. The component instantiation can be done by three forms. 1) instantiation of a component 2) instantiation of entity, and 3) instantiation of configuration. The syntax is,

instance_name : component_name port map ([ port_name => ] expression {, [ port_name => ] expression } ); Example 1 : Two input NAND gate

-- component declaration

component ND2

port (A, B : in BIT; C : out BIT);

end component;

. . .

signal X, Y, Z: BIT;

. . .

component instantiation by using different forms

U1 : ND2 port map (X, Y, Z); -- positional U2 : ND2 port map (A => X, C => Z, B => Y); -- named U3 : ND2 port map (X, Y, C => Z); -- mixed

Example shows the component instantiation statement defining a simple netlist. The three instancesU1, U2, and U3are instantiations of the 2-input XOR gate component declared in Example Fig. 5.6.1 illustrates the resulting design.

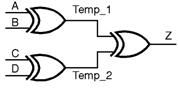

Example 2 : Boolean Logic

expressed in the form of logic gates

component xor2

port(A, B : in BIT; C : out BIT);

end component;

. . .

signal TEMP_1, TEMP2: BIT;

. . .

U1 : xor2 port map (A, B, TEMP_1);

U2 : xor2 port map (C, D, TEMP_2);

U3 : xor2 port map (TEMP_1, TEMP_2, Z);