Home > Digital CMOS Design > Propagation Delay > Delay Estimation

Delay Estimation

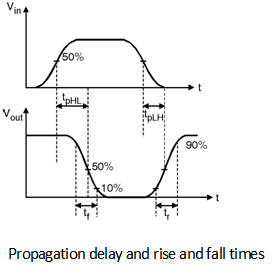

Delay Estimation : The propagation delay (tp) of a gate is defined as the time taken by a gate to respond when there is change on its inputs. It expresses the delay experienced by a signal when passing through a gate. It is measured between the 50% transition points of the input and output waveforms as shown in below Figure for an inverter.

As a gate shows different response times for rising or falling input waveforms the propagation delay is defined by two terms.

The tpLH defines the response time of the gate for a low to high output transition while tpHL refers to high to low transition. The propagation delay (tp) is defined as the average of these two times :

i.e. tp = tpLH + tpHL2

The propagation delay is function of both circuit technology and the style of the circuit. Also the delay is function of the slopes of the input and output signals of the gate. In order to consider this effect the terms rise time (tr) and fall time (tf) are introduced.

The rise and fall times are defined between the 10% and 90% points of the waveform as shown in Fig. 7.9.1. The rise and fall times of a signal are determined by the strength of the driving gate and the load connected to it.