Home > VHDL > Logic Circuits > 4 1 Mux using Different Modeling Styles

6.2.3 VHDL Code of 4:1 Mux using Different Modeling Styles :

-- Behavioral Modeling of 4:1 mux

library ieee;

use ieee.std_logic_1164.all;

entity MUX4_1 is

port ( Sel : in std_logic_vector(1 downto 0);

A, B, C, D : in std_logic;

Y : out std_logic );

end MUX4_1;

architecture behavior of MUX4_1 is

begin

process (Sel, A, B, C, D)

begin

if (Sel = "00") then

Y<= A;

elsif (Sel = "01") then

Y<= B;

elsif (Sel = "10") then

Y<= C;

else

Y<= D;

end if;

end process;

end behavior;

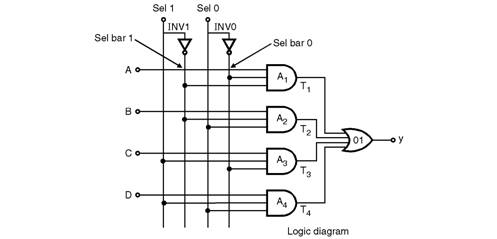

-- Structural modeling of 4:1 mux

library ieee;

use ieee.std_logic_1164.all;

entity MUX4_1 is

port ( Sel0,Sel1 : in std_logic;

A, B, C, D : in std_logic;

Y : out std_logic );

end MUX4_1;

architecture structural of MUX4_1 is

component inv

port (pin : in std_logic;

pout :out std_logic);

end component;

component and3

port (a0,a1,a2: in std_logic;

aout:out std_logic);

end component;

component or4

port (r0,r1,r2,r3:in std_logic;

rout:out std_logic);

end component;

signal selbar0,selbar1,t1,t2,t3,t4: std_logic;

begin

INV0: inv port map (Sel0, selbar1);

INV1: inv port map (Sel1, selbar1);

A1: and3 port map (A, selbar0, selbar1, t1);

A2: and3 port map (B, Sel0, selbar1, t2);

A3: and3 port map (C, selbar0, Sel1, t2);

A4: and3 port map (D, Sel0, Sel1, t4);

O1: or4 port map (t1, t2, t3, t4, Y);

end structural;

-- Dataflow modeling of 4:1 mux

architecture dataflow of MUX4_1 is

signal selbar0,selbar1,t1,t2,t3,t4: std_logic;

begin

selbar0<=not sel0;

selbar1<=not sel1;

t1<=A and selbar0 and selbar1;

t2<=B and sel0 and selbar1;

t3<=C and selbar0 and sel1;

t4<=D and sel0 and sel1;

Y<= t1 or t2 or t3 or t4;

end dataflow;