Home > VHDL > Counters > 8 bit Loadable Counter

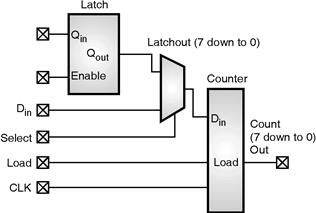

2.13.5 8 bit Loadable Counter using Generate statement :

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity counter is

port (Din :in std_logic_vector (7 downto 0);

Syncin:in std_logic_vector (7 downto 0);

load:in std_logic;

sel :in std_logic;

clk :in std_logic;

enable:in std_logic;

Count_out:buffer std_logic_vector (7 downto 0));

end counter;

architecture behav of counter is

signal counter:std_logic_vector (7 downto 0);

signal latchout:std_logic_vector (7 downto 0);

component latch is

port (Din, enable:in std_logic;

Qout:inout std_logic);

end component;

begin

Count_out <= counter(7 downto 0);

--Here, we map 8 instances of our latch with a FOR loop.

--Note: The label sync. Each FOR loop must have a unique label.

sync: for i in 0 to 7 GENERATE

latch_load: latch port map (Din(i), enable, latchout(i));

end GENERATE sync;

process

begin

wait until clk'Event and clk = '1';

if (load = '1' and sel = '0') then

counter<= latchout;

elsif (load = '1' and sel = '1') then

counter<= Syncin;

else

counter <= counter + 1;

end if;

end process;

end behav;

Note- The following latch code is necessary to compile above program

library ieee;

use ieee.std_logic_1164.all;

entity latch is

port ( Din: in std_logic;

enable: in std_logic;

Qout: inout std_logic );

end latch;

architecture behavior of latch is

begin

process (Din, enable)

begin

if enable = '1' then

Qout <= Din;

end if;

end process;

end behavior;